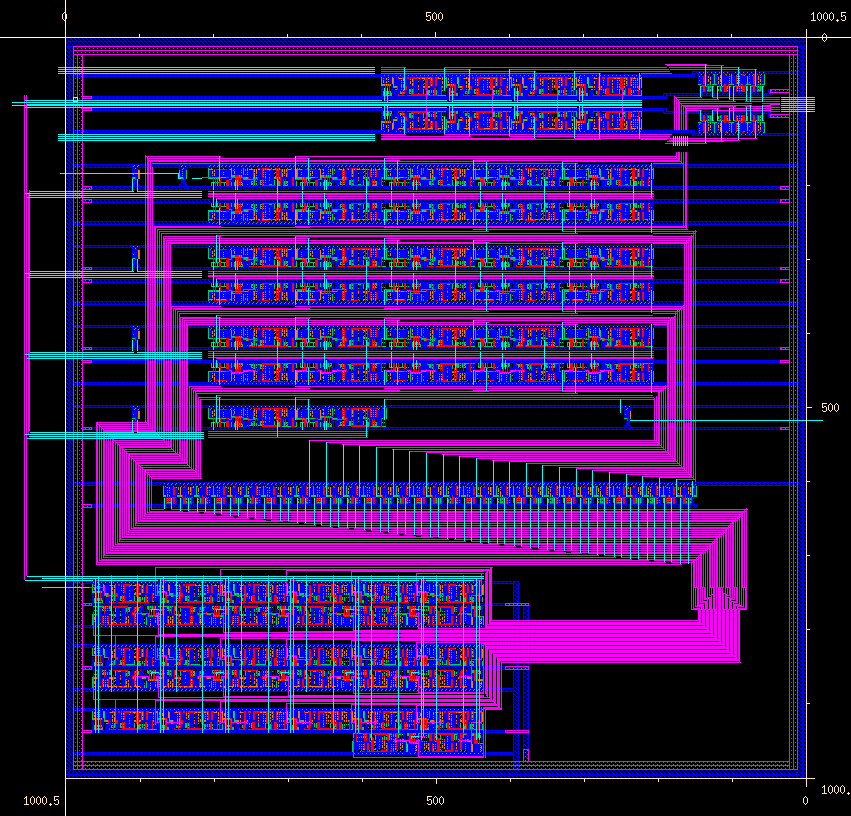

As a result, either version can replace multiple ICs in current designs, affording a single-chip solution that makes many applications practical for the first time. The chip has the processing power to handle many of the most sophisticated DSP algorithms needed in telecommunications, speech and image processing, and general industry applications. The more » processor relies on high-speed CMOS technology and a parallel architecture to start an instruction every 125 ns. Two versions of such a DSP chip are planned, one with and one without data ROM and program memory, and the latter has been cast in silicon. In the next stage of their evolution, DSP chips will have to rely on faster IC technologies and even greater degrees of parallel operation. The devices were fortified with Harvard-like parallel architecture, multiplication-accumulation hardware, and instruction pipelines. When standard microprocessors, constrained by their von Neumann architectures and weak arithmetic ability, proved inadequate for the task, the first specialized chips appeared. The course of digital signal processing is well plotted into the future. The lessons learned in this project were extended to the successful development of two high temperature versions of the LEON3 and a companion 8 Kbyte SRAM, a 200 C version for the Navy and a 275 C version for the gas industry. Yield data is presented for all, the HC11, SPI-RAM and ROM. The HC11 controller IC chip set is implemented more » in the Peregrine Semiconductor 0.5 micron Silicon-on-Sapphire (SOS) process using a custom high temperature cell library developed at Oklahoma State University. A SPI RAM IC completes the chip set and allows data RAM to be added in 4 kbyte increments. To avoid mask programmed internal ROM, a boot program is used to load the microcomputer program from an external mask SPI ROM.

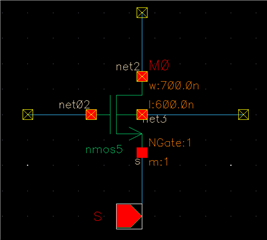

The chip is code compatible with the single chip mode commercial 68HC11 except for the absence of the analog to digital converter system. This extreme temperature version of the 68HC11 enables new high temperature designs and additionally allows 68HC11-based well logging tools and MWD tools to be upgraded for high temperature operation in deep gas reservoirs, The microcomputer chip consists of the microprocessor ALU, a small boot ROM, 4 kbyte data RAM, counter/timer unit, serial peripheral interface (SPI), asynchronous serial interface (SCI), and the A, B, C, and D parallel ports. The 68HC11 microprocessor is widely used in well logging tools for control, data acquisition, and signal processing applications and was the logical choice for a downhole controller. An HC11 controller IC and along with serial SRAM and ROM support ICs chip set were developed to support a data acquisition and control for extreme temperature/harsh environment conditions greater than 275 C.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed